2024-10-25 15:25:00

www.techspot.com

In brief: Nvidia has been quietly using the RISC-V architecture to power numerous computing devices, and deploying a substantial number of cores to paying customers. In fact, the company is nearing a historical milestone in terms of RISC-V core deployments.

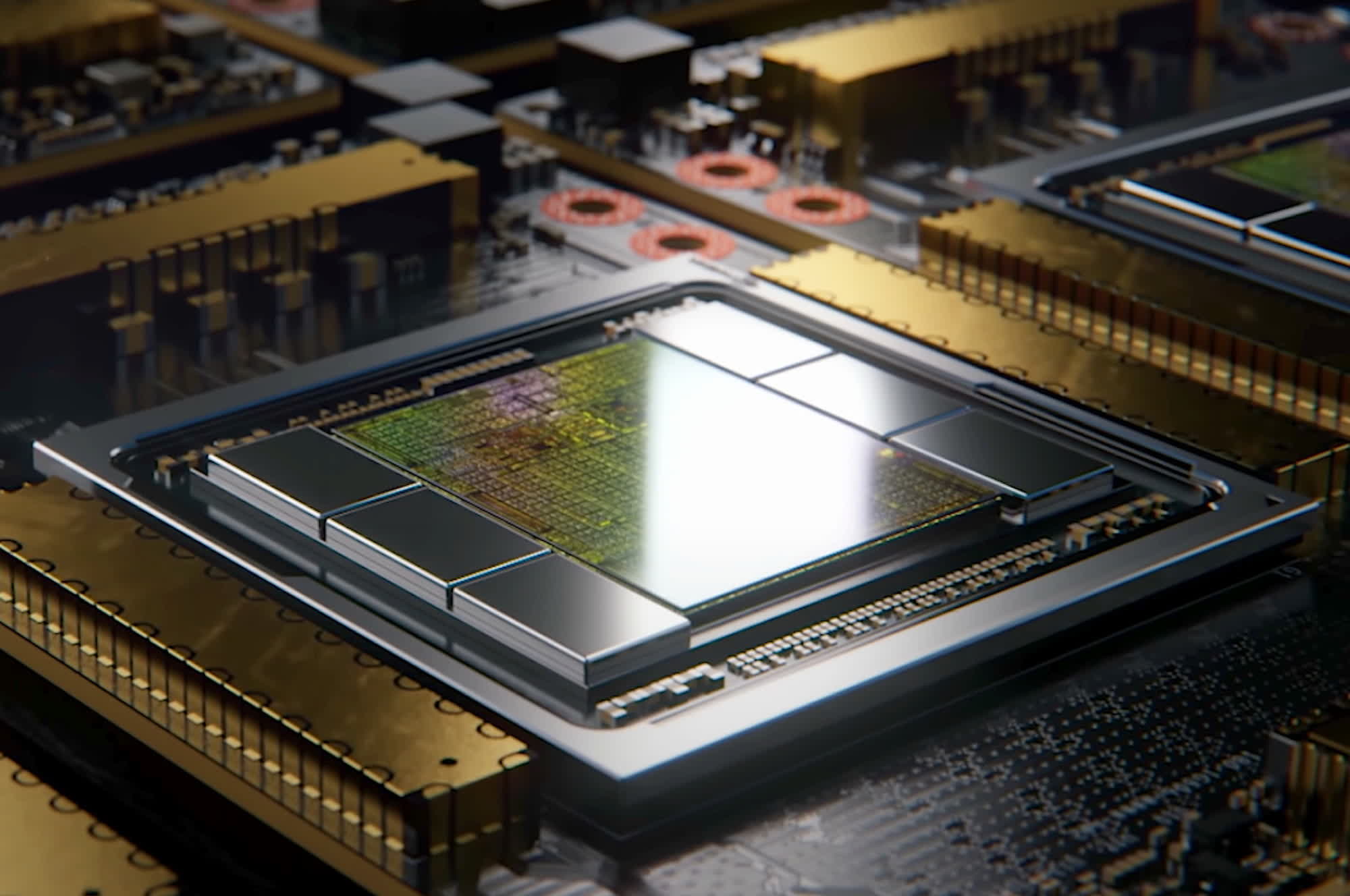

Nvidia has apparently been utilizing the RISC-V architecture for quite some time. As one of the most valued technology companies in the world, the GPU giant employs this open standard instruction set architecture (ISA) from the RISC paradigm in many of the custom, albeit “ancillary,” cores embedded within its GPUs.

Nvidia’s close relationship with RISC-V was highlighted at the recently held RISC-V Summit, where the company discussed how the open ISA is implemented in its chips. RISC-V-based cores have been used as specialized microcontroller units (MCUs) since 2015, replacing the company’s proprietary “Falcon” MCUs.

Fascinating talk at the #RISCV summit from Nvidia. Apparently there are between 10 and 40 #RISCV cores in every Nvidia chip, with Nvidia alone having shipped around a billion #RISCV cores pic.twitter.com/Uiy62YnnUy

– Nick Brown (@NickBrownHPC) October 22, 2024

Nvidia explained that the hardware and software for these RISC-V MCUs were developed in-house, and the number of cores continues to grow.

According to an “unofficial” estimate, the Santa Clara corporation is projected to ship around one billion RISC-V cores by the end of the year. RISC-V applications in Nvidia products encompass “function-level control” scenarios, including video codecs, display management, chip-to-chip interfaces, chip-level control tasks like power management and security, and network data processing.

Nvidia’s RISC-V cores feature more than 20 custom extensions. The most significant piece of silicon based on the open ISA is likely the GPU System Processor (GSP). Some GPUs include a specialized GSP unit that offloads GPU initialization and management tasks, thereby managing computing processes traditionally handled by the system’s CPU driver.

The GSP embedded in recent Nvidia GPUs offloads kernel driver functions, further reducing CPU utilization and enabling multiple remote users to share the same GPU unit in cloud environments. In addition to GPUs, Nvidia is also shipping RISC-V cores and MCUs in CPUs, System-on-Chip designs, and other products.

The RISC-V architecture began its journey in 2010 as a project at the University of California, Berkeley. Since 2019, the Swiss-based non-profit organization RISC-V International has been managing the development of the ISA. The architecture is available under a Creative Commons or BSD license, allowing anyone in the world to theoretically develop new chip designs based on it – and many are doing just that.

Support Techcratic

If you find value in Techcratic’s insights and articles, consider supporting us with Bitcoin. Your support helps me, as a solo operator, continue delivering high-quality content while managing all the technical aspects, from server maintenance to blog writing, future updates, and improvements. Support Innovation! Thank you.

Bitcoin Address:

bc1qlszw7elx2qahjwvaryh0tkgg8y68enw30gpvge

Please verify this address before sending funds.

Bitcoin QR Code

Simply scan the QR code below to support Techcratic.

Please read the Privacy and Security Disclaimer on how Techcratic handles your support.

Disclaimer: As an Amazon Associate, Techcratic may earn from qualifying purchases.

![Spigen Tempered Glass Screen Protector [GlasTR Slim] designed for Tesla Model S…](https://techcratic.com/wp-content/uploads/2024/11/61TVb0o8-tL._AC_SL1200_-360x180.jpg)

![Under Screen Storage Box for Tesla Model 3/Y 2017-2024, [Hidden Design & More Privacy]…](https://techcratic.com/wp-content/uploads/2024/11/61Wgffn93-L._AC_SL1500_-360x180.jpg)